Digital continuity, consistency and interoperability along the product life-cycle using graph-based design languages

Dr. Stephan Rudolph, University of Stuttgart, Germany

# GLOBAL PRODUCT DATA INTEROPERABILITY SUMMIT 2023

PDES. Inc.

BOEING is a trademark of Boeing Management Company Copyright © 2023 Boeing. All Rights Reserved Copyright © 2023 Elysium Inc. All Rights Reserved Copyright © 2023 Northrop Grumman Corporation. All Rights Reserved Copyright © 2023 Parker-Hannifin Corporation. All Rights Reserved Copyright © 2023 Parker-Hannifin Corporation. All Rights Reserved Copyright © 2023 PDES. All Rights Reserved

### **Bio Stephan Rudolph**

Global Product Data Interoperability Summit | 2023

Stephan Rudolph

#### education

Dipl.-Ing. / Dr.-Ing. / Priv.-Doz. (venia legendi) in Aerospace Engineering from University of Stuttgart, Germany

#### profession

- aerospace engineering faculty member, email <u>rudolph@ifb.uni-stuttgart.de</u>

- lectures on digital product design, art and science of systems architecting, design languages and algorithms, digital engineering, artificial intelligence

- adjunct associate professor, Swinburne University of Technology, Melbourne, Australia

- principal investigator in multiple German and European research projects

- design theory and similarity mechanics group head, academic supervisor of currently 21 PhD students

- more than 160 publications

- co-founder of Ingenieurgesellschaft f

ür Intelligente L

ösungen und Systeme mbH, a small German high-tech company (see <u>www.iils.de</u>)

- expert on graph-based design languages

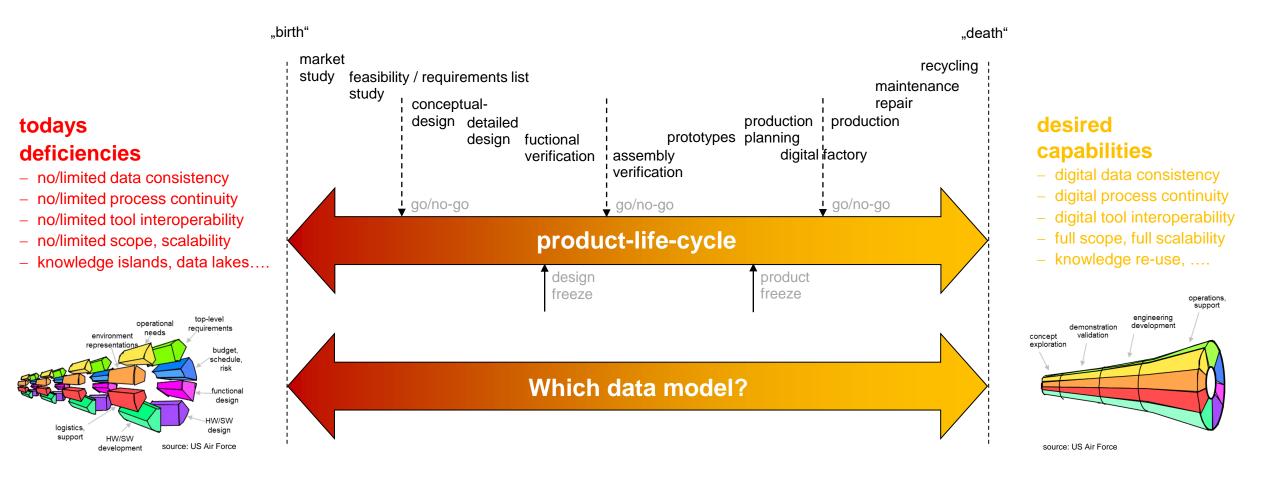

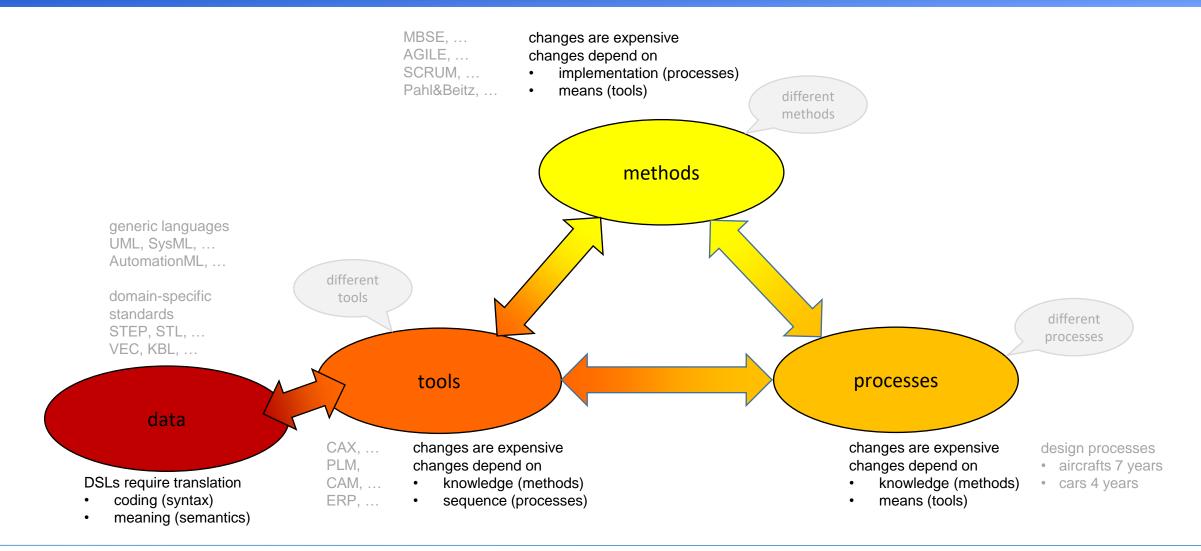

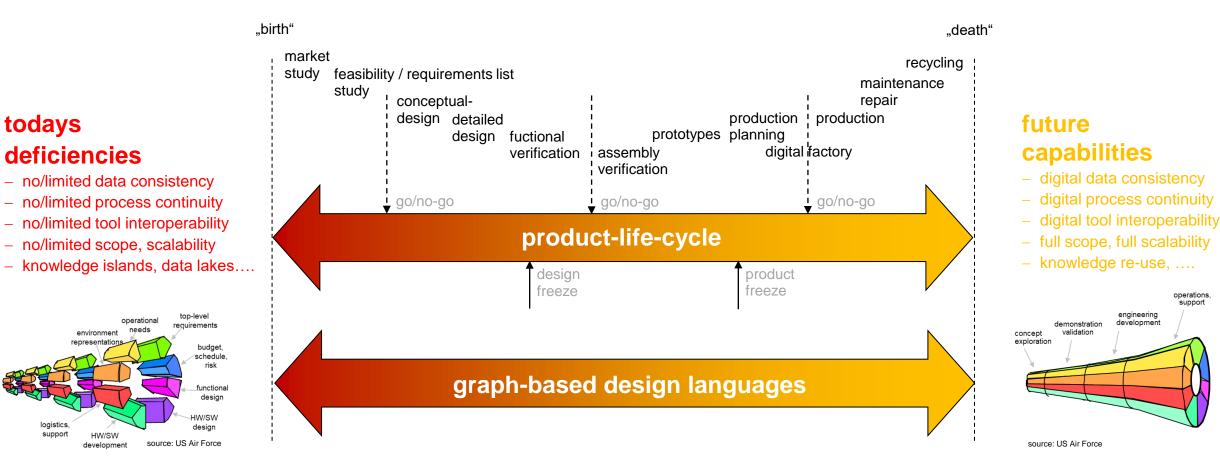

### Which Data Model solves the Problem of Digital Continuity, Consistency and Interoperability?

### **Engineering Problem Analysis (1 of 2)**

### **Engineering Problem Analysis (2 of 2)**

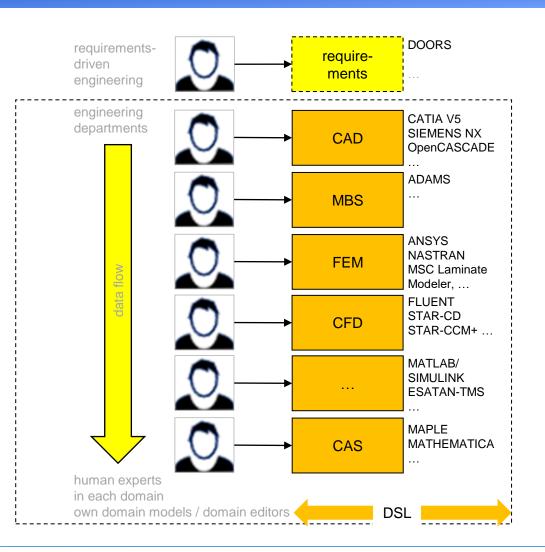

Global Product Data Interoperability Summit | 2023

disadvantages/deficiencies (from computer science perspective)

- existing multitude of domain editors  $\rightarrow$  no single source of truth

- data flow in iterative design loops  $\rightarrow\,$  revision management

- design loops/iterations  $\rightarrow$  manual rework

- models in DSLs  $\rightarrow$  vendor lock-in

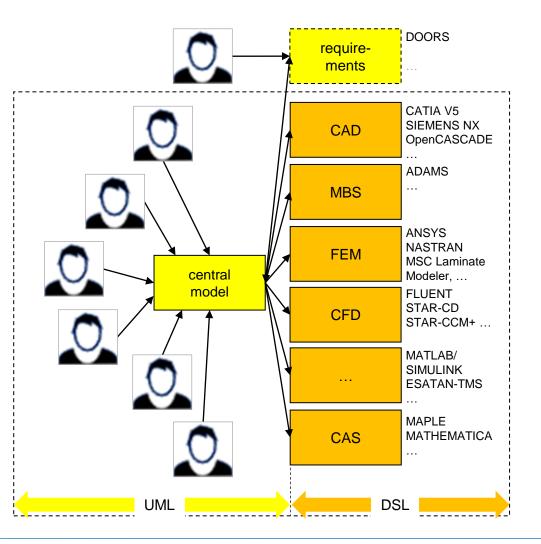

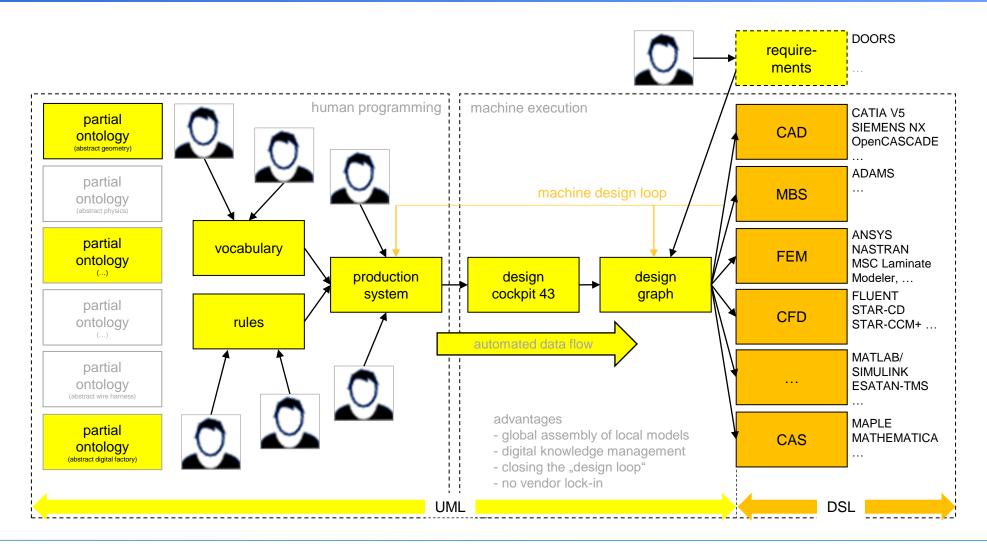

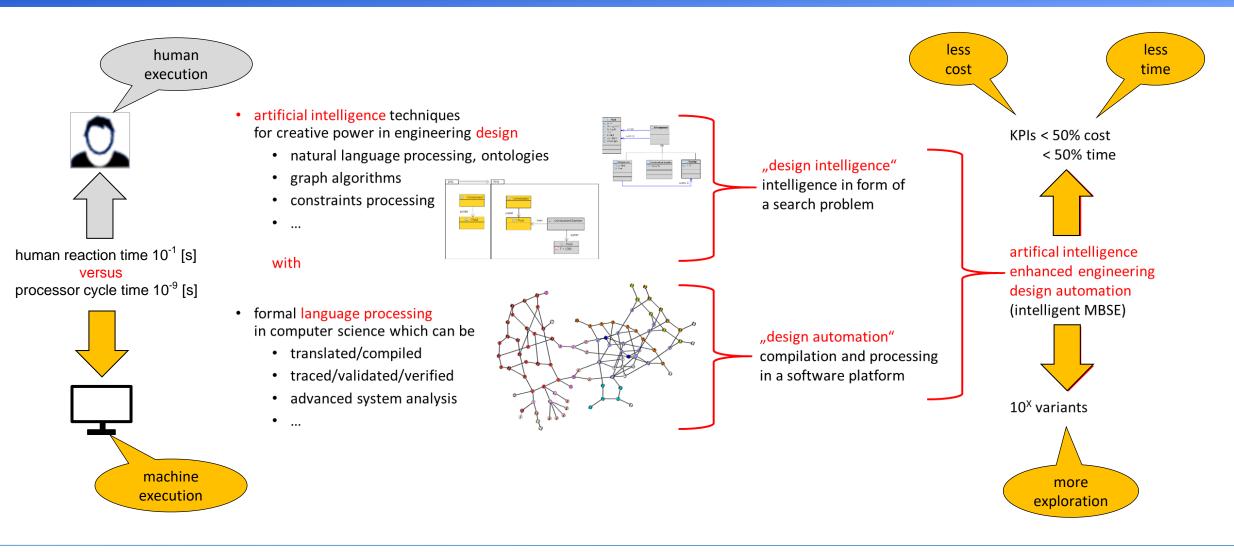

## **Engineering Solution (1 of 2)**

Global Product Data Interoperability Summit | 2023

advantages

- engineering data consistency through central model mapping

- use of generic object-oriented modeling language (here: UML)

disadvantages

- engineering design information flow needs to be reorganized

- engineers must be trained in new way of thinking / working

## **Engineering Solution (2 of 2)**

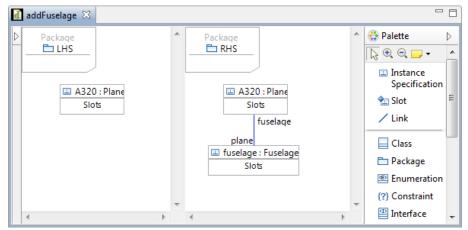

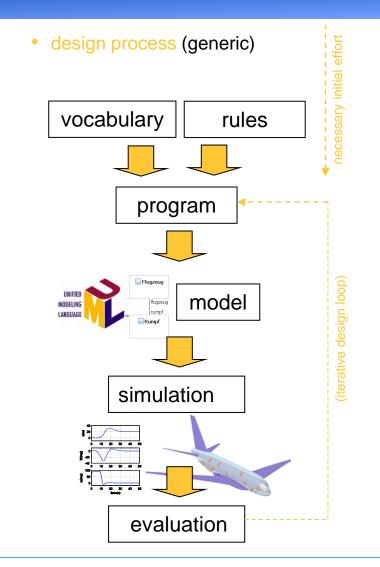

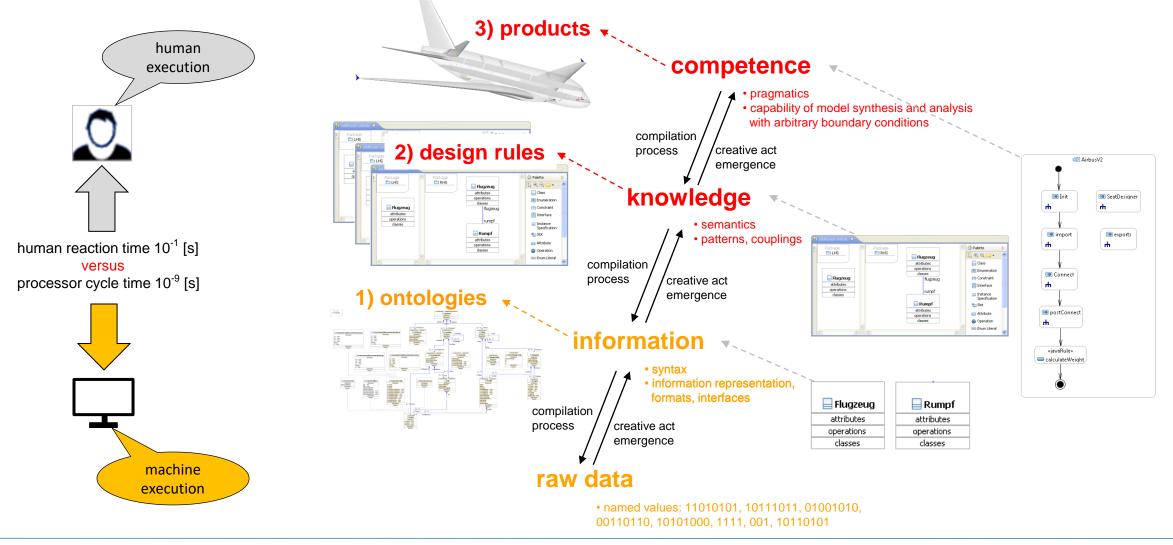

### **Graph-Based Design Languages (in UML)**

Global Product Data Interoperability Summit | 2023

vocabulary (UML classes)

| Plane      | E Fuselage |

|------------|------------|

| attributes | attributes |

| operations | operations |

| classes    | classes    |

• rules (UML model-transformations)

• production system (UML activity diagram) consists of a sequence of design rules

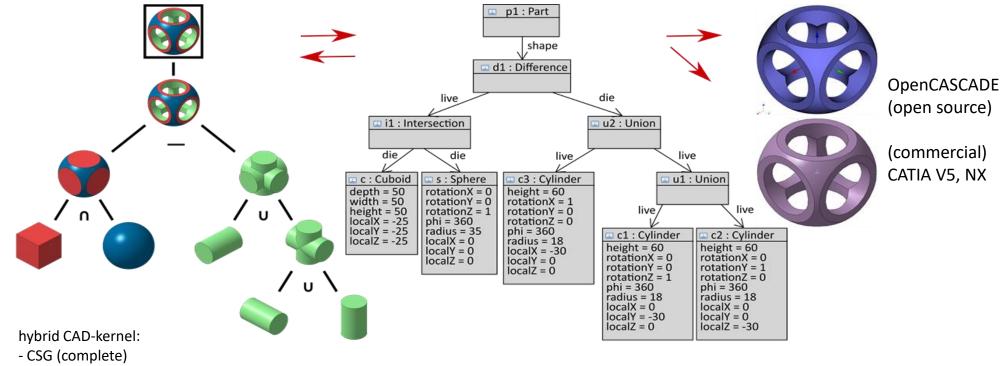

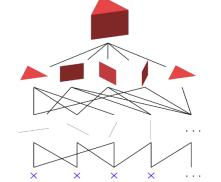

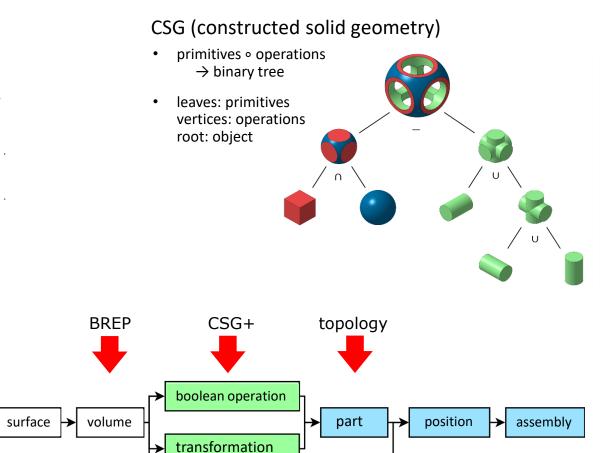

### Graph-Based Design Languages (Abstract Geometry, Part 1)

Global Product Data Interoperability Summit | 2023

CSG (constructed solid geometry)

- BREP (work in progress)

### Graph-Based Design Languages (Abstract Geometry, Part 2)

Global Product Data Interoperability Summit | 2023

### BREP (boundary representation)

| points         |               |    |       | lines         |          |          |

|----------------|---------------|----|-------|---------------|----------|----------|

| point number   | Х             | Y  | Ζ     | edge number   | vertex 1 | vertex 2 |

| 1              | 4             | 0  | 0     | 1             | 1        | 2        |

| 2              | -1            | 3  | 0     | 2             | 2        | 3        |

| 3              | -1            | -3 | 0     | 3             | 3        | 1        |

| 4              | 4             | 0  | 4     | 4             | 4        | 5        |

| 5              | -1            | 3  | 4     | 5             | 5        | 6        |

| 6              | -1            | -3 | 4     | 6             | 6        | 4        |

|                |               |    |       | 7             | 1        | 4        |

|                |               |    |       | 8             | 2        | 5        |

|                |               |    |       | 9             | 3        | 6        |

| surfaces       |               |    |       | volumes       |          |          |

| surface number | edge sequence |    | uence | volume number | surfaces |          |

| 1              | 123           |    | 3     | 1             | 12345    | 5        |

| 2              | 456           |    | 6     |               |          | _        |

| 3              | 1847          |    | 47    |               |          |          |

| 4              |               | 28 | 59    |               |          |          |

| 5              |               | 37 | 69    |               |          |          |

line

point

import

hybrid CAD-kernel:

- CSG (complete)

- BREP (work in progress)

primitive

→

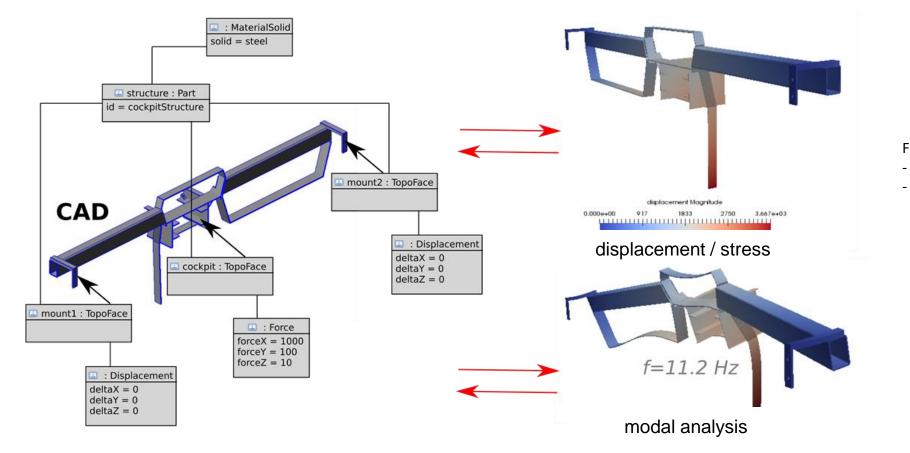

### **Graph-Based Design Languages (Abstract Physics)**

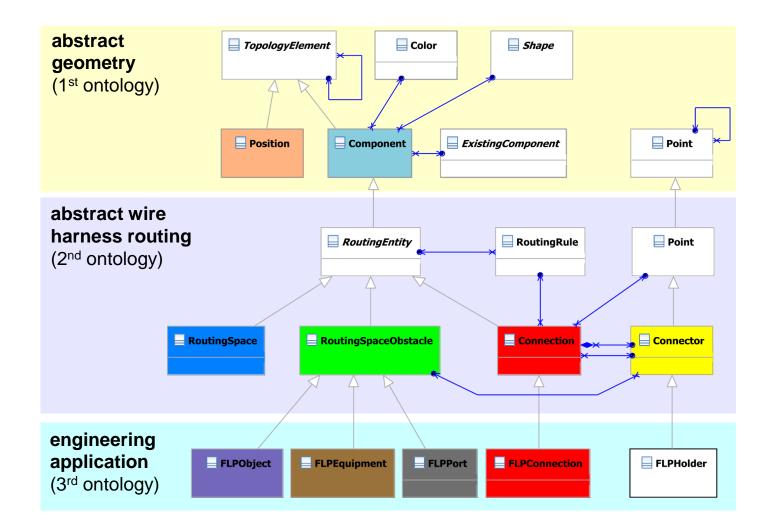

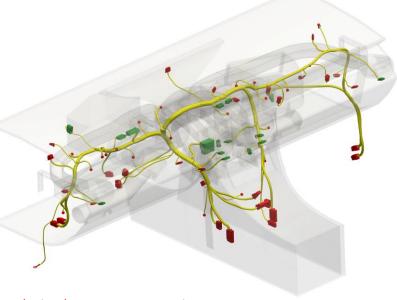

### Graph-Based Design Languages (Abtract Wire Harness and Ontology Mapping)

Global Product Data Interoperability Summit | 2023

#### design languages properties

- graph-based representation

- digital consistency

- digital continuity

- digital interoperability

video automotive cockpit: CAD/FEM/3D wire harness routing

#### ontology mapping

- via UML modeling mechanisms

- via UML model transformations (M2M, M2T)

©2018 Design Theory and Similarity Mechanics Group, University of Stuttgart (picture & video)

### **Graph-Based Design Languages (in UML)**

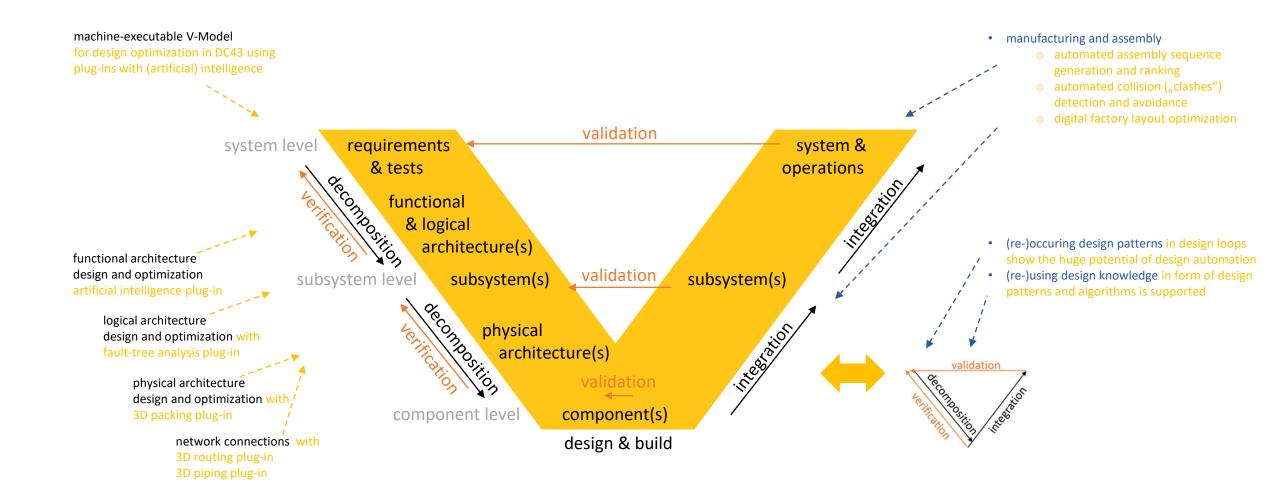

### Machine-Executable V-Model of MBSE with Graph-Based Design Languages

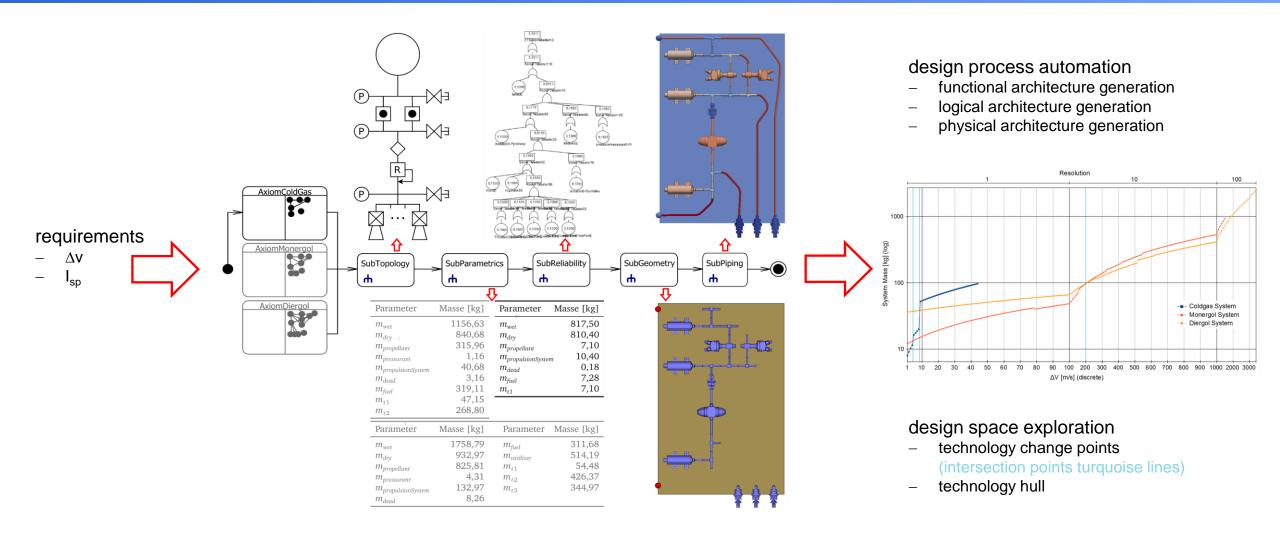

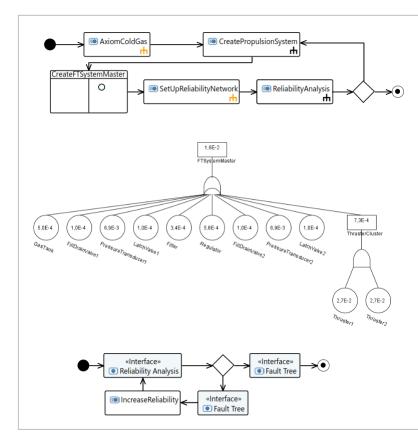

### Machine-executable V-Model of Satellite Propulsion System

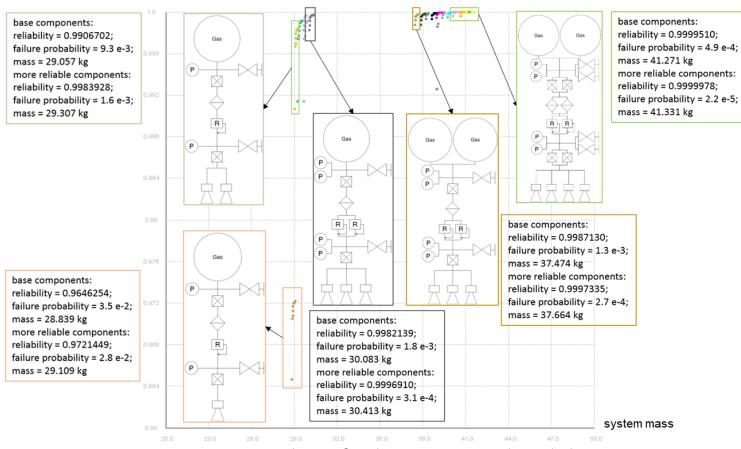

### Logical Architecture Generation with FTA-Plug-In (Engineering as a Service)

Global Product Data Interoperability Summit | 2023

© 2020 by Marius Riestenpatt gen. Richter. Modeled, programmed and generated using graph-based design languages with fault-tree analysis (FTA)-Plugin

reliability

DoE study courtesy © 2020 by Marius Riestenpatt gen. Richter. For details see: Riestenpatt gen. Richter, M. and Rudolph, S.: A scientific discourse on creativity and innovation in the formal context of graph-based design languages. 13th Anniversary "Heron Island" Conference Workshop on Computational and Cognitive Models of Creative Design (HI'19), Heron Island, Queensland, Australia, December 15–18, 2019.

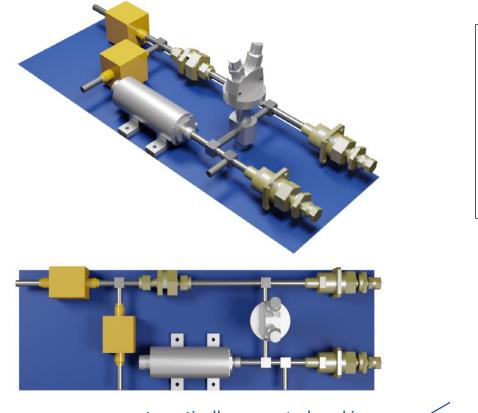

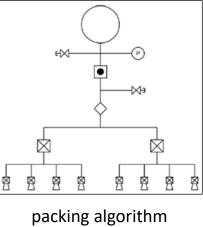

### Physical Architecture Generation with 3D Packaging Plug-In (Engineering as a Service)

Global Product Data Interoperability Summit | 2023

automatically generated packing (bendings forbidden, area 457 cm<sup>2</sup>)

to physical architecture w/o side-constraints

automatically generated packing

(bendings allowed, area 361 cm<sup>2</sup>)

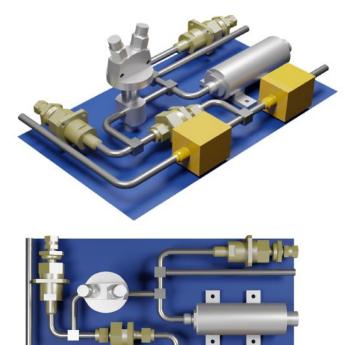

### Physical Architecture Generation with 3D Piping Plug-In (Engineering as a Service)

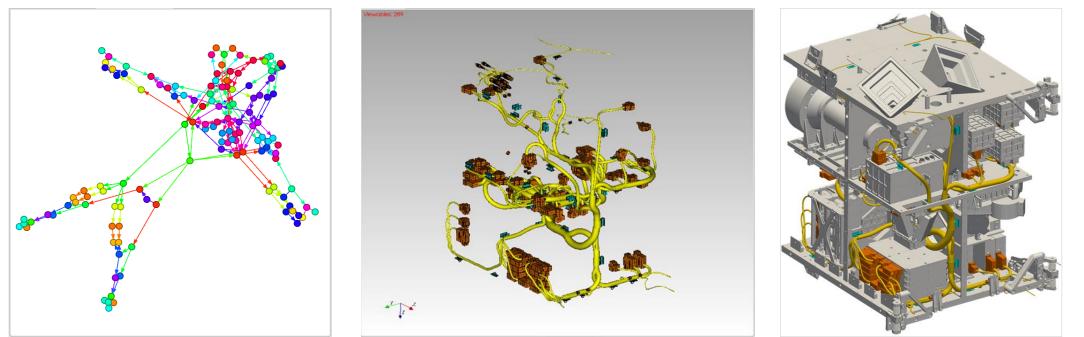

### Physical Architecture Generation with 3D Routing Plug-In (Engineering as a Service)

Global Product Data Interoperability Summit | 2023

© 2018 design graph of wire harness generated with 3D routing plug-in

harness shown was automatically generated in 15 mins on PC with i5@3,2GHz, 32GB RAM

CAD model courtesy © 2018 Institute for Space Systems, University of Stuttgart with integrated wire harness automatically generated with 3D routing plug-in

in the MANUNET project FORTIFIER (MNET20/ICT-3763)

- a data converter to STEP AP242 with EWIS content was implemented, including a mapping of VEC to STEP AP242

- a digital factory simulation for wire harness manufacturing was generated

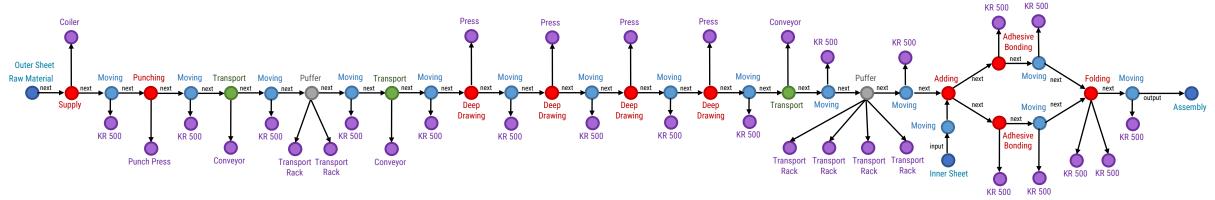

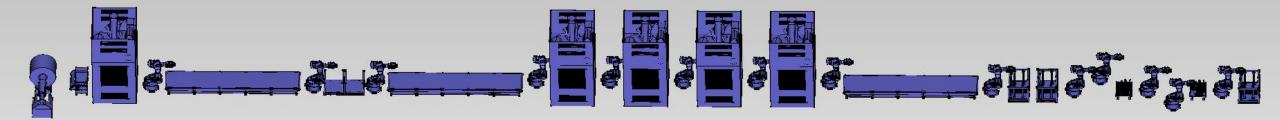

### **Digital Factory Generation with Digital Factory Plug-In (Engineering as a Service)**

Global Product Data Interoperability Summit | 2023

#### digital factory generation using design languages

- 2D layout generation, throughput design of transfer line

- generation of digital factory simulation

- VR-capabilities using HTC VIVE

© 2020 Modeled, programmed and generated with design languages using digital factory plug-in

### **Graph-Based Design Languages**

### **Philosophical Foundation of Formal Languages for Design**

Global Product Data Interoperability Summit | 2023

The philosopher William Brian Arthur postulated in his book<sup>1</sup> "The Nature of Technology" (2009) in chapter 5.2 entitled "Design as Expression Within a Language":

- A new device or method is put together from the available components - the available vocabulary – of a domain. In this sense a domain forms a language; and a new technological artifact constructed from components of the domain is an utterance in the domain's language.

- And it means that the key activity in technology engineering design – is a form of composition. It is an expression within a language (or several).

<sup>1</sup>Arthur, W.B.: The Nature of Technology - What It Is and How It Evolves. New York, Free Press, 2009.

## Graph-Based Design Languages provide Digital Continuity, Consistency and Interoperability

Global Product Data Interoperability Summit | 2023

\_

\_

Global Product Data Interoperability Summit | 2023

This research and development project was partly funded by the German Federal Ministry of Education and Research (BMBF) under the research program "Future of Value Creation" (program/funding code: MNET20/ICT-3763) and is supervised by the Project Management Agency Karlsruhe (PTKA).

The responsibility for the content of this publication lies solely with the author.

Dieses Forschungs- und Entwicklungsprojekt wurde teilweise mit Mitteln des Bundesministeriums für Bildung und Forschung (BMBF) im Forschungsprogramm "Zukunft der Wertschöpfung" (Programm/Förderkennzeichen: MNET20/ICT-3763) gefördert und vom Projektträger Karlsruhe (PTKA) betreut.

Die Verantwortung für den Inhalt dieser Veröffentlichung liegt allein beim Autor.